Рейтинг: 4.0/5.0 (1904 проголосовавших)

Рейтинг: 4.0/5.0 (1904 проголосовавших)Категория: Windows: Бенчмарки, тесты

Россиянин разогнал AMD FX-8350 до 8615 МГц

Пока заботы по организации московского финала AOOC 2014 не похитили всё свободное время у российского энтузиаста slamms и сотрудника местного представительства Asus в его же лице, он решил освежить рейтинг абсолютных частот, достигнутых процессорами AMD модели FX-8350. Имеющийся в распоряжении экземпляр процессора смог пройти валидацию CPU-Z на частоте 8615 МГц с восемью активными ядрами!

Белорусскому оверклокеру удалось обновить рекорд разгона AMD FX-60

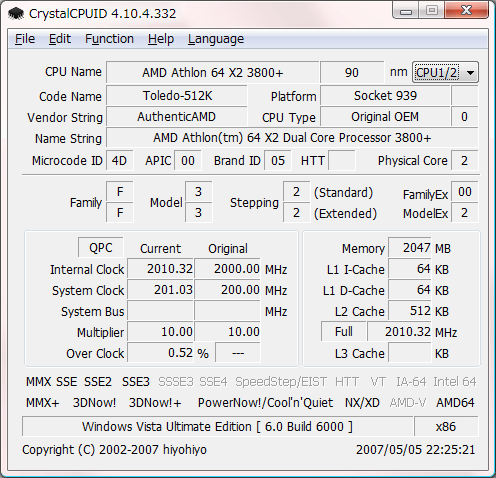

Иногда давно изученные любителями экстремального разгона компоненты удивляют обывателей много лет спустя. Это произошло и с двухъядерным процессором AMD FX-60 поколения Toledo (90 нм) в исполнении Socket 939, который оказался в распоряжении белорусского оверклокера Max1024 вместе с материнской платой DFI – LanParty NF4Ultra-D, резервуаром для жидкого азота Koolance CPU-LN2-V2 и памятью Geil Ultra-X типа DDR. Показать полностью..

Процессор энтузиаст из Могилёва смог разогнать до 3898,8 МГц, что является новым мировым рекордом частоты для данной модели. Предыдущее лучшее достижение принадлежало сильнейшему оверклокеру Норвегии. Правда, в абсолютном рейтинге частот достигнутый 90-нм процессором рубеж числится лишь на 7391-ом месте, но следует с уважением относиться к возрасту этого процессора.

Как можно догадаться, процессор охлаждался жидким азотом.

Сам автор рекорда, помимо фотографий тестового стенда и использованных компонентов, делится ещё и скриншотом CPU-Z (см рис).

Максим входит в пятёрку сильнейших оверклокеров Беларуси по версии HWBot и состоит в "национальной команде" по оверклокингу. Остаётся пожелать автору дальнейших успехов на поприще поиска "скрытых сокровищ разгона".

Начиная с процессоров Pentium появилась новая инструкция CPUID. по которой любая программа на любом уровне привилегий в любой момент времени могла получить ту же информацию, что и BIOS после сброса, и, вдобавок, 32-битный набор флагов расширений базовой архитектуры, реализованных в данном процессоре. Полученную информацию программа может использовать, например, для выбора исполняемого кода, оптимального для данного процессора (или отказа исполнения на "недостойном" ее процессоре), а также для настройки констант программных реализаций задержек. Инструкция CPUID была реализована и в ряде поздних моделей процессоров класса 486. Формат инструкции практически безгранично расширяем, с ее помощью процессор может выдавать хоть весь свой словесный портрет (если эту возможность заложат его разработчики). Однако информация для CPUID "зашивается" в процессор на этапе изготовления кристалла, что не позволяет, например, "выпытать" у процессора его официальную тактовую частоту (она определяется позже — на этапе тестирования уже готового процессора). А эта информация была бы полезна при борьбе с пиратским разгоном (перемаркировкой) процессоров, что, в общем-то, волнует изготовителя.

Следующий шаг, уже явно нацеленный на учет и контроль, был сделан в процессоре Pentium II Xeon. Здесь имеется специальная постоянная (только для чтения) память процессорной информации PIROM. которая хранит такие данные, как электрические спецификации ядра процессора и кэш-памяти (диапазоны частот и питающих напряжений), S-спецификацию (степпинг) и 64-битный серийный номер процессора. Кроме того, имеется энергонезависимая память Scratch EEPROM, которая предназначена для занесения системной информации поставщиком процессора (или компьютера с этим процессором) и может быть защищена от последующей записи. Для взаимодействия с PIROM и Scratch EEPROM (а также устройством термоконтроля) процессор имеет дополнительную последовательную шину SMBus (System Management Bus) — отдельный электрический интерфейс, с которым работает чипсет системной платы. Обращение к этим учетным данным получается довольно сложным — это целая процедура, привязанная к реализации чипсета, а не одна инструкция.

И, наконец, в Intel решили соединить всеобщий учет (и контроль) с простотой доступа: в процессор Pentium-3 ввели расширение инструкции CPUID. по которому легко можно получить 64-битный уникальный идентификатор данного процессора. Идентификатор процессора, по замыслу Intel, должен стать дополнительным средством аутентификации в сети Internet (и других сетях), наряду с именем пользователя и паролем, вводимыми вручную. Однако, если имя и пароль можно сменить в любое время, идентификатор присваивается навечно и принудительно, хотя имеется возможность запретить процессору сообщать свой идентификатор. Вот эта всеобщая инвентаризованность и вызвала бурю обсуждений прав на частную жизнь пользователей нового процессора. После жарких споров фирма Intel "идя навстречу пожеланиям трудящихся" постановила, что по умолчанию выдача идентификатора запрещена, а разрешается только с ведома пользователя. Как подчеркивает Intel, идентификатор сообщается пассивно, то есть компьютер с новым процессором, ОС и броузером не кричит на весь мир "я — номер такой-то!". Это естественно, поскольку для идентификации процессор должен исполнить фрагмент программного кода, в котором вызывается инструкция CPUID и интерпретируются ее результаты.

Для управления выдачей идентификатора в модельно-специфичном регистре BBL_CR_CTL (MSR 119h) выделяется запрещающий бит (бит 21). Он может быть установлен в "1" программно — с помощью инструкции обращения к MSR, и тогда по инструкции CPUID будет доступна только традиционная информация. Заметим, что инструкции обращения к MSR обычно привилегированы, т. е. могут выполняться только на уровне привилегий ядра ОС. По аппаратному сбросу процессора (и только так!) бит обнуляется, и полная идентификация разрешается. Декларированное "отключение по умолчанию" возлагается на ОС, и для Windows предлагается специальная утилита, опрашивающая значение бита MSR и управляющая его установкой, а также сообщающая прочитанный (по возможности) идентификатор. Для использования ОС, отличных от Windows, Intel рекомендует разработчикам BIOS включать фрагмент кода аналогичного назначения в BIOS Setup (здесь любое переключение будет требовать перезагрузки).

Основная информация о процессоре предоставляется по инструкции CPUID. доступность которой определяется через бит 21 (ID) регистра EFLAGS. По инструкции CPUID (0) можно определить производителя процессора и возможности данной инструкции. Вызов CPUID (1) сообщает сигнатуру процессора — тип, семейство, модель и степинг (таблица 1 ), а также список расширений архитектуры (таблица 2 ). Как видно из таблицы 1. одному и тому же сочетанию типа, семейства и модели может соответствовать несколько типов процессоров — например, Pentium-2 и Pentium-2 Xeon по ним неразличимы. Эти процессоры различаются элементами системы кэширования, и их можно распознать по дескрипторам (таблица 3 ), сообщаемым по CPUID (2). И, наконец, серийный номер процессора, если это позволено (см. ниже), можно узнать по CPUID (3). Серийный номер появился с процессорами Pentium 3 (он был введен еще в кристалл Celeron модели 6, но на конечном этапе производства эту возможность отключали).

Заметим, что здесь нигде в явном виде не фигурирует тактовая частота процессора — для каждой модели и степинга выпускаются процессоры с некоторым диапазоном тактовых частот, а конкретное значение обозначается на корпусе после отбраковочных испытаний. В процессорах Xeon "официальная" тактовая частота заносится в энергонезависимую память конфигурации, откуда может быть считана по интерфейсу SMBus. Доступ к этой памяти осуществляется по процедурам, определяемым чипсетом системной платы, но не по одной определенной инструкции процессора. Возможно, тактовую частоту можно определить и по серийному номеру процессора, но пока на это нет официальных указаний.

Идентификация процессора требуется на разных уровнях ПО. Первым делом идентификацию выполняет BIOS — для того, чтобы сообщить о найденных процессорах пользователю и выполнить необходимые настройки под конкретную модель и степинг процессора. Для процессоров 6-го поколения эта информация позволяет определить, какими ошибками (erratum) страдает данный процессор и какими "заплатками" эти ошибки нейтрализуются. Нейтрализация ошибок может выполняться как с помощью модификации микрокода процессора (update microcode), так и специфическими фрагментами программного кода для обработчиков прерываний и исключений. Эти "заплатки" могут входить как в операционные системы, так и в BIOS. Если конкретный процессор "не знаком" для BIOS или ОС, "заплатки" для него не будут загружены и возможны различные неожиданности при работе. В этом случае стоит позаботиться об обновлении BIOS (для флэш-BIOS это технически несложно) или приобретении загружаемых "заплат" для ОС.

В зависимости от обнаруженного процессора, ОС может использовать те или иные варианты реализации своих функций. ОС защищенного режима (а теперь иными практически и не пользуются) разрешает или запрещает те или иные архитектурные расширения (в основном записью в регистр CR4). Прикладным программам остается только согласиться с предлагаемым набором свойств процессора или отказаться от работы. Прикладные программы могут получать информацию о процессоре по инструкции CPUID при любом уровне привилегий, а привилегированные программы (PL=0) могут пользоваться и данными CR4.

Идентификация процессоров пользовательскими программами Рассмотрим возможности идентификации процессоров разных поколений. Программам, загружаемым операционной системой, да и самой ОС информация о процессоре из регистра EDX недоступна (аппаратный сброс был слишком давно). Задача идентификации осложняется тем, что поколение процессора заранее неизвестно. Когда появился процессор 80286, его (и все последующие) отличали от 8086/88 по значениям, сохраняемым в стеке инструкцией PUSH SP: первые процессоры сначала декрементировали указатель стека, а потом его сохраняли. Для идентификации процессоров, начиная еще с 16-разрядных, рекомендуется анализ значения регистра флагов, сохраненного по инструкции PUSHF после попытки его изменения. Приведем параметры регистра флагов в том порядке, в каком их анализируют при идентификации типа:Для определения присутствия сопроцессора выполняют инструкцию FNINIT, после чего исполняют инструкцию FNSTENV и проверяют корректность образа сопроцессора, сохраненного в памяти. Тип сопроцессора обычно определяется типом CPU, кроме процессора 80386, который может работать как с 80287, так и с 80387. Их различить можно по способу представления +бесконечность и –бесконечность: у 287 они одинаковы, у 387 — различны.

Инструкция CPUID. доступная, начиная с Pentium и некоторых моделей 486, вызывается с параметром, указанным в регистре EAX. Значение EAX при вызове CPUID. указанные в скобках, определяет функцию вызова:

Вызов CPUID (2) появился с процессорами 6-го поколения. Пока что по нему сообщаются только дескрипторы элементов кэширования (таблица 3 ). Например, для Pentium Pro по CPUID (2) возвращается EAX=03020101h, EBX=0, ECX=0, EDX=06040A42h. Это означает, что вызов нужно делать однократно (AL=1); TLB инструкций для страниц 4К имеет 32 вхождения (01h), для страниц 4М — 2 вхождения; TLB данных для страниц 4К на 64 вхождения (03h), для страниц 4М — на 8 вхождений (04h); первичный кэш инструкций — 8К (06h), данных — 8К (0Ah); вторичный кэш 256К (42h). CPUID (3) — получение младших 64 бит серийного номера процессора (Intel Processor Serial Number), доступно начиная с Pentium III (семейство 6, модель 7 и старше). EDX — средние 32 бита идентификатора; ECX — младшие 32 бита идентификатора. Полный идентификатор имеет длину 96 бит. Старшие 32 бита — код идентификации процессора, возращаемый в EAX по CPUID (1). Доступность вызова определяется по биту PN регистра свойств (после CPUID (1) бит EDX.18=1). После аппаратного сброса у процессоров, поддерживающих сообщение идентификатора, этот вызов разрешен. Запретить сообщение идентификатора до следующего аппаратного сброса можно установкой в единицу бита 21 регистра. Фрагмент программы на ассемблере для запрета сообщения номера приведен ниже. После запрета бит PN обнуляется. Снова разрешить сообщение номера программно невозможно, повторное разрешение возможно только через аппаратный сброс (по сигналу RESET, но не INIT#).

Вызовы инструкций CPUID с EAX>3 (в пределах разрешенного значения, сообщенного процессором при вызове CPUID (0) зарезервированы для будущих применений.

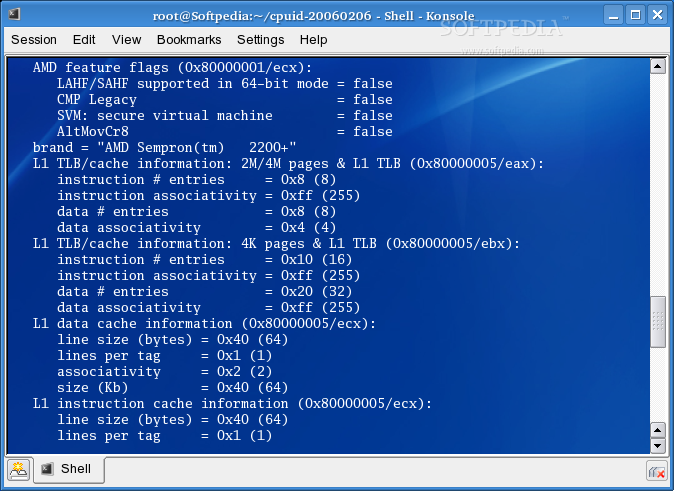

Фирма AMD расширила вызовы CPUID. Для проверки наличия расширений вызывается CPUID с EAX=8000_0000h. При наличии расширений в EAX результатом будет число, большее 8000_0000h, — максимальный параметр расширенного вызова. Вызовом EAX=8000_0001h можно определить специфические расширения архитектуры от AMD. Например, поддержка 3DNow! определяется по установленному биту 31 регистра EDX.

Назначение флагов расширения архитектурыPrior to using the CPUID instruction, you should also make sure the processor supports it by testing the 'ID' bit (0x200000) in eflags. This bit is modifiable only when the CPUID instruction is supported. For systems that don't support CPUID, changing the 'ID' bit will have no effect.

Note: Implementing this routine in for example C can lead to issues, because the compiler may change EFLAGS at any time.

This assembly routine checks if CPUID is supported:

Note 1: There are some old CPUs where CPUID is supported but the ID bit in EFLAGS is not (NexGen). The are also CPUs that support CPUID if and only if it has to be enabled first (Cyrix M1).

Note 2: You can simply attempt to execute the CPUID instruction and see if you get an invalid opcode exception. This avoids problems with CPUs that do support CPUID but don't support the ID bit in EFLAGS; and is likely to be faster for CPUs that do support CPUID (and slower for CPUs that don't).

Basic usageThe idea of the CPUID instruction is that you can call it with different values in EAX, and it will return different information about the processor. For example, if we want the Vendor ID String (see below), we should code something like that:

CPU Vendor ID StringWhen called with EAX = 0, CPUID returns the vendor ID string in EBX, EDX and ECX. Writing these to memory in this order results in a 12-character string. These can be tested against known Vendor ID strings:

You already know that the Vendor ID String is returned in EBX, ECX, EDX. Let us take an Intel processor. It should return "GenuineIntel". Look at the following text to see how the string is placed in the registers:

Also, EAX is set to the maximum EAX value supported for CPUID calls, as not all queries are supported on all processors.

CPU FeaturesWhen called with EAX = 1 (CPUID_GETFEATURES), CPUID returns a bit field in EDX containing the following values. Note that different brands of CPUs may have given different meanings to these. Recent processors also use ECX for features (which form a different set), with which you should be very careful as some old CPUs return bogus information in this register.

An array of four integers that contains the information returned in EAX, EBX, ECX, and EDX about supported features of the CPU.

RequirementsThis intrinsic stores the supported features and CPU information returned by the cpuid instruction in cpuInfo. an array of four 32-bit integers that is filled with the values of the EAX, EBX, ECX, and EDX registers (in that order). The information returned has a different meaning depending on the value passed as the function_id parameter. The information returned with various values of function_id is processor-dependent.

The __cpuid intrinsic clears the ECX register before calling the cpuid instruction. The __cpuidex intrinsic sets the value of the ECX register to subfunction_id before it generates the cpuid instruction. This enables you to gather additional information about the processor.

For more information about the specific parameters to use and the values returned by these intrinsics on Intel processors, see the documentation for the cpuid instruction in Intel 64 and IA-32 Architectures Software Developers Manual Volume 2: Instruction Set Reference and Intel Architecture Instruction Set Extensions Programming Reference. Intel documentation uses the terms "leaf" and "subleaf" for the function_id and subfunction_id parameters passed in EAX and ECX.

For more information about the specific parameters to use and the values returned by these intrinsics on AMD processors, see the documentation for the cpuid instruction in AMD64 Architecture Programmer's Manual Volume 3: General-Purpose and System Instructions and in the Revision Guides for specific processor families. AMD documentation uses the terms "function number" and "subfunction number" for the function_id and subfunction_id parameters passed in EAX and ECX.

When the function_id argument is 0, cpuInfo[0] returns the highest available non-extended function_id supported by the processor. The processor manufacturer is encoded in cpuInfo[1]. cpuInfo[2]. and cpuInfo[3].

Support for specific instruction set extensions and CPU features is encoded in the cpuInfo results returned for higher function_id values. For more information, see the manuals linked above, and the following example code.

Some processors support Extended Function CPUID information. If this is supported, function_id values from 0x80000000 might be used to return information. To determine the maximum meaningful value allowed, set function_id to 0x80000000. The maximum value of function_id supported for extended functions will be written to cpuInfo[0].

cpuid - Dump CPUID information for each CPU

cpuid [options. ]

Descriptioncpuid dumps detailed information about the CPU (s) gathered from the CPUID instruction, and also determines the exact model of CPU (s) from that information.

It dumps all information available from the CPUID instruction. The exact collection of information available varies between manufacturers and processors. The following information is available consistently on all modern CPUs: It also produces synthetic fields based on information from multiple CPUID functions. Currently, the synthetic fields are the exact model of each CPU (but see LIMITATIONS below) as (synth); the multiprocessing characteristics including the number of cores per chip (c) and the number of hyperthreads per core (t) as (multi-processing synth); and a decoding of the APIC physical ID as (APIC synth).

The determination of the model is based on the following information: The determination of the multiprocessing characteristics and decoding of APIC physical ID is based on the following information: In addition, a simpler and coarser determination of the CPU is performed using only the information listed above under version information (1/eax). It is provided as (simple synth) under version information (1/eax). However, it tends to be unable to distinguish between various modern CPUs.

cpuid accepts the following command line arguments: -1, --one-cpu Display information only for the first CPU. This cuts down on the output on a multiprocessor system, and is useful when certain that all CPUs are identical. -f FILE. --file=FILE Read raw hex information from FILE instead of from executions of the cpuid instruction. -h, -H, --help Display help information. -i, --inst Use the CPUID instruction. The information it provides is reliable. It is not necessary to be root to use this option. (This option is the default.) -k, --kernel Use the CPUID kernel module. The information does not seem to be reliable on all combinations of CPU type and kernel version. Typically, it is necessary to be root to use this option. -r, --raw Display only raw hex information with no decoding. -v, --version Display cpuid version.

LimitationsThere are numerous cases where there is no way to distinguish between various CPUs in the (synth) information. In some cases, the sizes of caches, number of cores, brand strings, etc. can be used to distinguish multiple CPUs with the same family and model. But there are cases where that information is insufficient. Whenever cpuid is unable to distinguish between multiple CPUs, it will list all known possibilities.

If you believe that a certain processor should be distinguishable from another and it isn't, please inform the author of this tool.

The (multi-processing synth) information is unreliable on many processors. It faithfully reports the information provided by the CPUID instruction and decodes it as recommended by the processor manufacturers, but often that information is incorrect. The information seems to indicate the architecture's capabilities, rather than what the particular chip actually does. In particular, it seems commonplace to claim the presence of multiple hyperthreads when there is only one.

Information SourcesInformation on the CPUID instruction and on specific CPUs is available from the following documents from Intel Corporation <http://www.intel.com/support/processors/index.htm >, with the specified Document Numbers:

241618: Intel Processor Identification and the CPUID Instruction, Application Note 485

242480: Pentium Processor Specification Update

242689: Pentium Pro Processor Specification Update

243326: 60- and 66-MHz Pentium Processor Specification Update

243337: Intel Pentium II Processor Specification Update

243748: Intel Celeron Processor Specification Update

243776: Intel Pentium II Xeon Processor Specification Update

243887: Mobile Intel Pentium II Processor Specification Update

244444: Mobile Intel Celeron Processor at 466 MHz, 433 MHz, 400 MHz, 366 MHz, 333 MHz, 300 MHz, and 266 MHz Specification Update

244453: Intel Pentium III Processor Specification Update

244460: Intel Pentium III Xeon Processor Specification Update

245306: Mobile Intel Pentium III Processor and Mobile Intel Pentium III Processor-M Specification Update

245421: Mobile Intel Celeron Processor (0.18u and 0.13u) Specification Update

249199: Intel Pentium 4 Processor Specification Update

249678: Intel Xeon Processor Specification Update

250721: Mobile Intel Pentium 4 Processor-M Specification Update

251309: Mobile Intel Celeron Processor on .13 Micron Process in Micro-FCPGA Package Specification Update

252665: Intel Pentium M Processor Specification Update

253176: Mobile Intel Pentium 4 Processor with 533 MHz System Bus Specification Update

276613: Detecting Multi-Core Processor Topology in an IA-32 Platform by Khang Nguyen and Shihjong Kuo

290741: Intel Xeon Processor MP Specification Update

290749: Intel Celeron Processor in the 478-Pin Package Specification Update

300303: Intel Celeron M Processor Specification Update

302209: Intel Pentium M Processor on 90nm Process with 2-MB L2 Cache Specification Update

302352: Intel Pentium 4 Processor on 90 nm Process Specification Update

302354: Intel Celeron D Processor 3xx Sequence Specification Update

302402: Intel Xeon Processor with 800 MHz System Bus

302441: Mobile Intel Pentium 4 Processor supporting Hyper-Threading Technology on 90-nm process technology Specification Update

306752: 64-bit Intel Xeon Processor MP with 1 MB L2 Cache Specification Update

306757: 64-bit Intel Xeon Processor MP with up to 8 MB L3 Cache Specification Update

306832: Intel Pentium Processor Extreme Edition and Intel Pentium D Processor Specification Update

309159: Dual-Core Intel Xeon Processor 2.80 GHz Specification Update

309222: Intel Core Duo Processor and Intel Core Solo Processor on 65 nm Process Specification Update

309627: Dual-Core Intel Xeon Processor 7000 Sequence Specification Update

311827: Intel Celeron D Processor 300 Sequence Specification Update

313065: Dual-Core Intel Xeon Processor 5000 Series Specification Update

313279: Intel Core 2 Extreme Processor X6800 and Intel Core 2 Duo Desktop Processor E6000 Sequence Specification Update

313356: Dual-Core Intel Xeon Processor 5100 Series Specification Update

314554: Dual-Core Intel Xeon Processor 7100 Series Specification Update

314916: Dual-Core Intel Xeon Processor 3000 Series Specification Update

313515: Intel Pentium Dual-Core Processor Specification Update

316134: Quad-Core Intel Xeon Processor 3200 Series Specification Update

316964: Intel Celeron Processor 400 Series Specification Update

316982: Intel Pentium Dual-Core Desktop Processor E2000 Series Specification Update

317667: Intel Celeron Processor 500 Series Specification Update

318081: Intel Xeon Processor 7200 and 7300 Series Specification Update

318547: Intel Celeron Processor 200 Sequence Specification Update

318585: Intel Xeon Processor 5400 Series Specification Update

318586: Intel Xeon Processor 5200 Series Specification Update

318727: Intel Core 2 Extreme Processor QX9000 Series and Intel Core 2 Quad Processor Q9000, Q9000S, Q8000, Q8000S Series Specification Update

318733: Intel Core 2 Duo Processor E8000 and E7000 Series Specification Update

318915: Intel Core 2 Duo Processor and Intel Core 2 Extreme Processor on 45-nm Process Specification Update

318925: Intel Celeron Dual-Core Processor E1000 Series Specification Update

319006: Dual-Core Intel Xeon Processor 3100 Series Specification Update

319007: Quad-Core Intel Xeon Processor 3300 Series Specification Update

319129: Intel Core 2 Extreme Processor QX9775 Specification Update

319536: Intel Atom Processor Z5xx Series Specification Update

319735: Intel Celeron Dual-Core Processor T1x00 Series Specification Update

319978: Intel Atom Processor 200 Series Specification Update

320047: Intel Atom Processor N270 Series Specification Update

320121: Intel Core 2 Extreme Quad-Core Mobile Processor, Intel Core 2 Quad Mobile Processor, Intel Core 2 Extreme Mobile Processor, Intel Core 2 Duo Mobile Processor, Intel Core 2 Solo Mobile Processor and Intel Celeron Processor on 45-nm Process Specification Update

320257: Intel EP80579 Integrated Processor Product Line Specification Update

320336: Intel Xeon Processor 7400 Series Specification Update

320468: Intel Pentium Dual-Core E6000 and E5000 Series Specification Update

320529: Intel Atom Processor 300 Series Specification Update

320767: Intel Core i7-900 Mobile Processor Extreme Edition Series, Intel Core i7-800 and i7-700 Mobile Processor Series Specification Update

320836: Intel Core i7-900 Desktop Processor Extreme Edition Series and Intel Core i7-900 Desktop Processor Series Specification Update

321324: Intel Xeon Processor 5500 Series Specification Update

321333: Intel Xeon Processor 3500 Series Specification Update

322166: Intel Core i7-800 and i5-700 Desktop Processor Series Specification Update

322373: Intel Xeon Processor 3400 Series Specification Update

322568: Intel Celeron Processor E3x00 Series Specification Update

322849: Intel Atom Processor N400 Series Specification Update

322861: Intel Atom Processor D400 Series (Single Core) Specification Update

322862: Intel Atom Processor D500 Series (Dual Core) Specification Update

322814: Intel Core i7-600, i5-500, i5-400 and i3-300 Mobile Processor Series Specification Update

322911: Intel Core i5-600, i3-500 Desktop Processor Series and Intel Pentium Processor G6950 Specification Update

323056: Intel Xeon Processor L3406 Specification Update

323179: Intel Core i7-660UE, i7-620LE/UE, i7-610E, i5-520E, i3-330E and Intel Celeron Processor P4505, U3405 Series Datasheet Addendum Specification Update

323105: Intel Xeon Processor C5500/C3500 Series Specification Update

323254: Intel Core i7-900 Desktop Processor Extreme Edition Series and Intel Core i7-900 Desktop Processor Series on 32-nm Process Specification Update

323338: Intel Xeon Processor 3600 Series Specification Update

323344: Intel Xeon Processor 7500 Series Specification Update

323372: Intel Xeon Processor 5600 Series Specification Update

323874: Intel Pentium P6000 and U5000 Mobile Processor Series Specification Update

324209: Intel Atom Processor E6xx Series Specification Update

324341: Intel Atom Processor N500 Series Specification Update

Intel 64 Architecture Processor Topology Enumeration (Whitepaper)

324456: Intel Celeron Mobile Processor P4000 and U3000 Series Specification Update

324643: 2nd Generation Intel Core Processor Family Desktop Specification Update

324827: 2nd Generation Intel Core Processor Family Mobile Specification Update

325122: Intel Xeon Processor E7-8800 / 4800 / 2800 Product Families Specification Update

325307: Intel Atom Processor Z600 Series Spefification Update

325630: Intel Atom Processor Z6xx Series Specification Update

326140: Intel Atom Processor N2000 and D2000 Series Specification Update

326198: Intel Core i7 Processor Family for the LGA-2011 Socket Specification Update

326510: Intel Xeon Processor E5 Family Specification Update

Information on the CPUID instruction and on specific CPUs is available from the following documents from Advanced Micro Devices, Inc. <http://www.amd.com/us-en/Processors/TechnicalResources >, with the specified Publication Numbers:

20734: AMD Processor Recognition Application Note

21266: AMD-K6 Processor Revision Guide Model 6

21641: AMD-K6-2 Processor Revision Guide Model 8

21846: AMD-K6 Processor Revision Guide Model 7

22473: AMD-K6-III Processor Revision Guide Model 9

23614: AMD Athlon Processor Model 4 Revision Guide

23865: AMD Duron Processor Model 3 Revision Guide

24332: AMD Athlon Processor Model 6 Revision Guide

24806: AMD Duron Processor Model 7 Revision Guide

25481: CPUID Specification

25703: AMD Athlon Processor Model 8 Revision Guide

25759: Revision Guide for AMD Athlon 64 and AMD Opteron Processors

26094: BIOS and Kernel Developer's Guide for AMD Athlon 64 and AMD Opteron Processors

27532: AMD Athlon Processor Model 10 Revision Guide

31177H: AMD Geode NX Processors Data Book

31610: Revision Guide for AMD NPT Family 0Fh Processors

33234F: AMD Geode LX Processors Data Book

41322: Revision Guide for AMD Family 10h Processors

41788: Revision Guide for AMD Family 11h Processors

44739: Revision Guide for AMD Family 12h Processors

47534: Revision Guide for AMD Family 14h Models 00h-0Fh Processors

48063: Revision Guide for AMD Family 15h Models 00h-0Fh Processors

Information on the CPUID instruction and on specific CPUs is available from the following documents from Transmeta Corporation <http://www.transmeta.com/crusoe_docs/Crusoe_CPUID_5-7-02.pdf >:

Processor Recognition, 2002/05/07

Information on generic hypervisor CPUID levels is available from this proposal: <http://lwn.net/Articles/301888/ >.

Information on KVM hypervisor CPUID levels is available from the Linux kernel under Documentation/kvm/cpuid.txt.

Information on Microsoft hypervisor CPUID levels is available from the following document from Microsoft: <http://msdn.microsoft.com/en-us/library/windows/hardware/ff542428%28v=vs.85%29.aspx >.

Also, information is available from the following web sites: <http://www.sandpile.org/ia32/cpuid.htm >

WARNING! This is a project that is still under construction. Both the code and the documentation are still being worked on. Feedback would be appreciated.

REQUEST: I would appreciate if you could run this on your machine and send me the resulting. cpuid file, so I can build a database of all kinds of machines for visibility. You can read the .cpuid file and assure yourself that no proprietary or confidential information is being transmitted.

The CPUID instruction is a fairly complex instruction. Its purpose is to return information about the processor properties. These can be useful for many purposes, including optimizing certain regular computations to take advantage of the properties of the cache. However, the discussion of how this is done is outside the scope of this article.

The CPUID instruction is a fairly complex instruction. Its purpose is to return information about the processor properties. These can be useful for many purposes, including optimizing certain regular computations to take advantage of the properties of the cache. However, the discussion of how this is done is outside the scope of this article.

The CPUID Explorer is designed to show you, in a graphical format, the informtion returned by the CPUID instruction, and when appropriate, it will decode the information and provide textual representations as well.

Like most of my projects, this project has two aspects: the actual CPUID instruction display, and a set of Windows programming techniques. The programming techniques are covered in a companion essay. (Note: as of 10-Mar-07, this essay has not been written)

Other things to note about the CPUID instruction is that it is a serializing instruction. That is, when it is executed, it stops all concurrent, speculative, and pipelined executions. All instructions which have been issued up to the point of the CPUID instruction must complete before the processor is permitted to proceed, and no instructions will be dispatched until the CPUID instruction has completed. The CPUID instruction is the only non-privileged serializing instruction available to user-level programmers (all other serializing instructions can only be executed in Ring 0, that is, in the kernel).

The most common usage of this is when the Time Stamp Counter (TSC ) is read directly by an application, using the RDTSC instruction. The RDTSC instruction is not a serializing instruciton, and consequently it is possible that some of the instructions which follow it have already been issued before the TSC is read, or existing instructions have not yet completed, thus resulting in an inaccurate measurement of the time interval. The proper way to use RDTSC is to precede it by a CPUID instruction so that no instructions are issued early and all instructions have completed.

The CPUID instruction overviewThe CPUID instruction is a non-privileged instruction, and can be called in user space. It nominally takes in the EAX register a code that tells what information should be returned, and returns values in the EAX. EBX. ECX and EDX registers.

There are two special exceptions to how CPUID is used. When the input parameter is 2, it returns information including how many times a CPUID with value 2 in EAX needs to be called to get all the relevant information. The other case is when the input parameter is 4, the value in the ECX register tells which cache level of information to deliver.

The CPUID Explorer is currently targeted only to 32-bit x 86 systems, because it uses inline assembly code to issue the CPUID instruction. The 64-bit compiler does not support inline assembly code insertions. The 64-bit compiler has an intrinsic __cpuid instruction, but unfortunately it is incorrectly implemented in the Microsoft compiler. It fails to load the ECX register (apparently the compiler writer never actually read the documentation on the CPUID instruction, or read only the first paragraph, and decided this was sufficient knowledge to do the implementation. )

The CPUID Explorer projectThis project has three components

This came about for a variety of reasons. One was an interest in modifying an algorithm to take advantage of cache strategies on a target architecture. Probably the most compelling reason for doing this was I needed something to occupy my time during a long overseas flight.

The CPUID ExplorerThe CPUID Explorer is a program which reads all of the relevant parameters it can using the CPUID instruction and displays them in a human-readable form. It allows you to readily see all the parameters the architecture is capable of telling you. Using this information, you can consider ways to utilize it. However, be aware that some of this is highly non-portable, and can be quite different on different architectures. The AMD architectures, for example, are quite different from the Intel architectures, and the CPUID instruction returns information in a different format for these architectures. So the problem is not necessarily straightforward. But this can provide a start.

Tab displayEach parameter to the CPUID instruction (nominally EAX. but sometimes EAX, ECX ) will display in a separate page. In some cases, the register displays are so detailed that only one register will sensibly fit on a single page.

The pages displayed by the CPUID instruction are shown below. Note, however, that on any given machine, the actual number of pages displayed may be different; on some machines the CPUID instruction does not support all the features shown in the snapshots here, and for those features not supported, the page will not be displayed.

To make it possible to create and debug this application, since I was doing the work largely on my laptop which has a limited CPUID repertoire, I have a special feature when it is compiled in Debug mode: all pages are displayed, but those which are unsupported are shown with all controls disabled. The information which displyed in these disabled pages is not meaningful, and this is solely done as an aid to the developer.

The following CPUID calls, which are all that are defined in the Intel and AMD documentation, are currently supported, when available.

The block diagramThe program attempts to construct a block diagram of the machine architecture. An example is shown below.

The left shows the number of logical CPU cores on the chip on which the program is running. The next group over displays the L1 cache. Then the number of bits of virtual address supported are shown. This is all displayed as part of the CPU box. Then the next grouping is the Translation Lookaside Buffers (TLBs) that handle the page translations, followed by the L2 cache parameters. If there is an L3 cache, it would appear next, but this architecture has no L3 cache, so the next box is the arrow showing the number of physical address lines available on the chip. The large white area is the physical memory, and there is not currently any support to fill this in; this will be in a future release of the program. More extensive flyover (tooltip) help will also be added.

Reading and writing CPUID filesIn addition to reading the CPUID information from the current processor, it is possible to write a data file which contains information about the current processor. This configuration file can be then read in to the program running on any other machine. This allows for remote support where CPU information may be relevant, particularly for a program that is trying to take advantage of the platform-specific information.

These operations are available via the system menu.

These operations are available via the system menu.

W rite CPUID info file is only available when there is no current CPUID information file. The file is in XML format and has the extension .cpuid .

R ead CPUID info file will read a previously-saved CPUID information file, which is a .cpuid file. It will read in the CPUID file and reconfigure the program to act as if it were running on that system. Only the tabs that would be visible on that machine are visible. Note that the ability to select which CPU the CPUID Explorer is running on is disabled.

Clo se CPUID info file closes the previously-open CPUID information file, and reverts to running on the current machine. It reconfigures the program to display only the relevant information for the current machine.

The GetCPUID functionThere is a module CPUIDx86.cpp. and its header file, CPUIDx86.h. which supports the 32-bit CPUID interface.

The type is the input parameter to the CPUID instruction. It is the value placed in the EAX register. The only values which are guaranteed to be supported on all architectures are 0 and 0x80000000. Each of these will return a value in EAX which is the largest permitted value for subsequent CPUID instructions.

Notationally, I will represent the call of the CPUID instruction with value n in the EAX register as CPUID(n ) .

The regs parameter is a pointer to the structure below.

The structure is nominally output-only, but the value of ECX in the structure will be loaded into the ECX register before doing the CPUID instruction. In all cases except code CPUID(4) this value is ignored by the instruction and overwritten, but for CPUID(4) it selects which cache parameter information is provided. The permitted values for CPUID(4) are 1, 2 and 3 for now; values 4..32 are reserved for future use. Value 0 is not a permitted value. Notationally, I will represent the call of CPUID(4) with value n as CPUID(4, n ) .

The call is specified to return FALSE if the CPUID instruction is unsupported. However, since there are no machines today that can run Windows that do not support the CPUID instruction, I have not implemented code to perform this test.

A typical set of calls might be

The Value Types and DisplaysThe values returned by the CPUID instruction are of these forms

The raw register values are always displayed in the window above the tabbed dialog. The interpreted register values are displayed in the appropriate tabbed dialog. Switching tabs causes the appropriate CPUID instruction to be executed at that point, and the values will change to represent this new execution.

Bit Field DisplayWhen a set of bit fields is used, the display looks similar to the one shown below. Each field is in a color, and its descriptive text is in the same color. The colors were chosen so that black text is readable against the color (ideally). This set of colors is fixed, but there is a table in the source code that can be changed to change the set of colors. The colors are used in a round-robin order from the known set of colors.

The values are displayed in decimal, unless suffixed by B indicating binary or H indicating hexadecimal.

Numeric displayWhen a numeric display is required, the value is displayed in decimal or hexadecimal.

When a textual display is required, the value is displayed as a quoted string. A character whose value is 0x00 is displayed as \0 .

When an entire register value is reserved, the contents are generally not displayed. When a bit field is reserved, its value is displayed, and the highlighting color for reserved fields always uses the same color.

Computed valueIn some cases, the value displayed is not overly useful. Instead, a meaningful value (such as a readable string) must be computed from the information displayed. Sometimes this is done by looking the value up in a table (the lookup strings are documented, and you may copy them from this project to one of your own if you need the displayed value), and sometimes it is done by a computation based on the value (concatenating bit fields, adding bit fields, or adding 1 to a bit field value are typical examples). These computed values will be displayed in addition to the information presented.

Platform displayIf the display is different on an Intel and AMD platform, the platform type will appear in the lower left corner of the window.

The Register Layout structuresWhenever a value in a register is a bit field, there is always an accompanying struct that defines the fields. The structs have canonical names based on which CPUID(n) code and register is used. Nominally the names are of the form Er Xnd . where r is the register name, <A. B. C. D >, n is the decimal value of the low-order byte of EAX used for the CPUID instruction, and d indicates if it is a basic or extended call

The following structures are defined

These will be examined in detail in the accompanying essay on the CPUID instruction.

The general structure of these structs is

To access the values, you assign the appropriate register contents from the selected register to the w member and read the values out from the structure member. The platform indicates the platform involved, and is one ofNote that in some cases, there are the same fields assigned for both Intel and AMD.

In this example, a test is made to see if the CMPXCHG16B instruction is supported on this architecture.

These structures cann be found in the file CPUIDRegs.h.

Sample displaysAt the top of the dialog is the common register information. The unlabeled box in the top left corner is the value of EAX on input to the CPUID instruction. The remaining four boxes are labeled with the register name of the register, and contain the output from the CPUID instruction. These are the "raw" register values. They are nearly unintelligible when bit fields are involved.

Note that in a multiprocessor system, you might want some assurance that these values are from a specific processor. The CPU selection is enabled for multiprocessors. This snapshot was taken from a uniprocessor. (It is actually unlikely you would get different values from a different CPU in the mix, because the requirements of Windows for Symmetric Multiprocessing, down to the step level of the silicon. On the other hand, if you are having trouble, this is a simple way to determine if you have violated this restriction with a heterogeneous mix of processors).

This illustrates several of the display styles. The contents of EAX are a simple integer, the maximum value of CPUID that is supported for this processor (this snapshot was deliberately done from the Debug version so all tabs are installed and visible). The values in EBX. ECX. and EDX are character strings, so are shown quoted. The resultant CPU type name is a computed value and is the concatenation of the three register values.

CPUID(1):EAX

This page illustrates a typical example of a display of fields. The fields and their labels are highlighted in matching colors, and the Reserved fields are all the same medium-dark gray color.

Note that the reserved fields are displayed in binary, the other fields, except the stepping ID, are displayed in hexadecimal, and the stepping ID is displayed in decimal. There is no ambiguity that 0000B might be the hexadecimal equivalent of 11 because in that case it would have been displayed as 0000BH. The processor type is also displayed in binary because that is how the documentation explains the values.

There are two computed fields shown here.

In this case, a documented algorithm for computing the model ID is used. The model ID is documented according to the following pseudo-code

As it turns out, the extended model number here is 0H so the computed model appears to be the same as the basic model, but the algorithm has been applied. This particular item will not be displayed if the family ID is other than 0x6 or 0xF .

The processor type is decoded according to a lookup table based on the documented processor types.

ToolTip Help

When a bit field is displayed, hovering the mouse over it will pop up a tool tip giving the bit field within the register, as shown below.

CPUID(1):ECX

This is another example of showing bit fields. In this case, the bit field descriptions are visually extended to the layout of the register. When feasible, the bits are grouped by nybbles.